[더구루=정예린 기자] 삼성전자와 미국 시놉시스가 차세대 반도체 패키징 기술 '칩렛' 생태계 강화에 한 발 더 다가섰다. 삼성전자는 글로벌 기업들과 협력을 통해 5나노미터(nm) 이하 공정의 설계자산(IP) 포트폴리오를 넓히며 파운드리 경쟁 우위를 확보하고 있다.

시놉시스는 6일(현지시간) "표준 패키징 기술을 지원하는 시놉시스의 UCIe(Universal Chiplet Interconnect Express) IP가 삼성전자의 5나노 응용 공정(SF5A)에서의 뛰어난 성능을 성공적으로 입증했다"며 "16GT/s의 속도에서 실행했으며 비트 에러율(BER)이 낮다는 사실을 확인했다"고 발표했다.

UCle는 개방형 칩렛 간의 연결 표준화를 위해 지난 2022년 출범한 컨소시엄이다. UCIe를 PCIe, USB, NVMe 등과 같은 새로운 연결 규격으로 수립하는 것이 목표다. 삼성전자와 SK하이닉스, TSMC, 인텔, AMD, Arm 등 반도체 회사와 구글 클라우드, 메타, 마이크로소프트(MS) 등 IT 기업 120여 개가 참여하고 있다. <본보 2022년 3월 3일 참고 [단독] 반도체 어벤저스 뭉쳤다…삼성·인텔·AMD, 개방형 칩렛 생태계 구축>

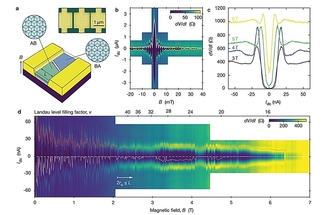

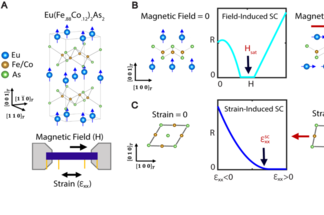

칩렛은 여러 개의 다이들을 연결해 하나의 반도체로 만드는 방식이다. 초미세공정 전환에 따른 기술적 한계를 극복할 대안으로 평가받으며 반도체 업체들의 관심을 한 몸에 받고 있다. 칩렛 구조 적용시 최신 미세 공정을 적용하지 않고 칩렛을 여러 개 붙이는 방식으로 코어 수를 늘릴 수 있다. UCIe 표준을 성립하면 다른 회사의 칩렛 구조와도 호환돼 비용 절감도 가능하다.

시놉시스의 UCle 솔루션은 컨트롤러, 물리계층(PHY), 검증 IP를 포함한다. 고대역폭·저전력·저지연의 다이 간 연결을 제공한다. 특히 UCle PHY는 여러 첨단 파운드리 공정에서 성능을 검증하고 타사 장치와의 성공적인 상호 운용성을 완료했다는 게 시놉시스의 설명이다.

삼성전자와 시놉시스는 작년 6월 파운드리 IP 포트폴리오 협력을 확대한다고 발표했다. 삼성전자의 3나노(SF3)·4나노(SF4)·5나노(SF5) 등부터 자동차용 애플리케이션을 지원하는 최신 공정인 SF5A·SF4A까지 시놉시스의 UCle, PCIe, USB 등 다양한 IP를 최적화하기로 했다. 약 1년여 만에 칩렛 표준 관련 기술적인 진전을 보이며 파트너십이 성과를 나타내고 있다.

한편 삼성전자는 파운드리 생태계 조성을 위해 IP 파트너십 구축에 힘쓰고 있다. 파운드리 기업의 IP 포트폴리오는 팹리스 업체가 위탁생산할 회사를 결정하는 데 핵심 요인 중 하나이기 때문이다. 칩 고도화에 따라 설계가 복잡해지면서 필요한 IP가 점차 늘어나자 팹리스 업체들은 비용과 시간을 절감하기 위해 IP 전문 회사를 적극 활용하고 있다. 삼성전자는 지난 2018년부터 파운드리 협업 생태계인 '세이프(Samsung Advanced Foundry Ecosystem, SAFE)'를 운영하며 케이던스, 시놉시스, 지멘스 등 75개 이상 파트너사들과 협력 중이다.