[더구루=정예린 기자] 삼성전자가 3nm(나노미터) 공정에 게이트올어라운드(GAA)를 기반으로 나노시트를 여러장 적층해 독자 개발한 'MBCFET(Multi Bridge Channel FET)'를 도입한다.

10일 업계에 따르면 송태중 삼성전자 상무는 최근 국제고체회로학회(ISSCC)에서 "삼성전자는 약 10년 동안 핀펫 트랜지스터를 사용해 왔지만 3나노 이하 공정에서는 GAA 방식을 사용한다"며 "새로운 트랜지스터는 더 작은 크기에도 고속과 저전력의 특성을 가진다"고 말했다.

삼성전자는 오는 2022년 3나노 이하 공정에서 MBCFET를 활용할 계획이다.

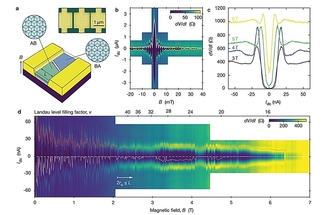

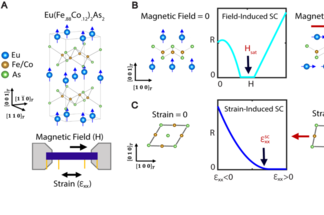

MBCFET는 가늘고 긴 와이어 형태의 GAA 구조에 종이처럼 얇고 긴 모양의 나노시트를 적층해 GAA의 한계를 극복한 삼성전자만의 독자 기술이다. 윗면-앞면-뒷면 등 총 3면을 트랜지스터의 게이트를 쓰는 핀펫 이후 개발돼 게이트의 아랫면까지 모두 쓰는 4차원 방식의 기술인 GAA에서 한 발 더 앞서 나간 것이다.

새로운 기술은 칩 면적, 소비전력, 속도 등에서 핀펫 대비 월등히 앞선다는 평가를 받고 있다. 트랜지스터 채널이 넓을수록 전압의 저항을 효과적으로 줄일 수 있는데 설계 유연성이 우수해 전력차단 능력도 뛰어나다.

삼성전자는 MBCFET가 7나노 핀펫 공정 대비 칩 면적과 소비전력을 각각 45%, 50% 줄일 수 있다고 밝혔다. 메모리 셀 상태를 전환하는 데 필요한 최소 전압이 크게 감소해 차세대 SRAM 개발에도 속도가 붙을 것으로 보고 있다. SRAM은 시스템반도체에서 캐시메모리(자주하는 작업이나 동작을 저장해두는 임시 기억공간)의 기능을 담당한다.

업계에서는 MBCFET 기술이 향후 소형화, 저전력 특성을 가진 더 높은 성능의 트랜지스터 개발을 앞당길 수 있을 것이라 기대하고 있다.

파운드리 업계 1위로 삼성전자와 초미세 공정 경쟁을 이어가고 있는 대만 TSMC는 3나노까지는 기존 핀펫 공정을 이용하고 2나노부터 GAA를 적용할 방침이다.