[더구루=오소영 기자] 삼성전자가 반도체 설계자산(IP) 업체 램버스와 고대역 메모리 'HBM2E' 솔루션용 IP를 자사 공정에서 검증했다. 반도체 설계 기업(팹리스)의 IP 접근성을 높이며 시스템반도체 생태계를 강화한다.

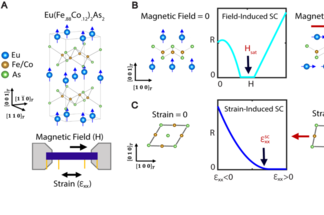

23일 업계에 따르면 삼성전자는 램버스가 개발한 14·11나노미터(nm·10억분의 1m) 핀펫 공정 기반의 HBM2E 솔루션용 IP를 검증했다. 램버스의 설계 라이선스가 삼성전자의 공정에서 잘 작동하는지 살폈다.

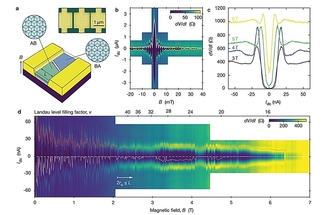

HBM2E는 기존 D램보다 데이터 처리 속도를 끌어올린 HBM의 차세대 제품이다. 램버스가 선보인 HBM2E 솔루션용 IP는 2.5D 패키징 기술을 적용한 반도체에 활용된다. 2.5D 패키징은 HBM과 시스템온칩(SoC)을 미세회로 기판인 실리콘 인터포저 위에 함께 집적하는 기술이다. 각각의 칩을 1개의 패키지 안에 배치해 전송 속도를 높이고 면적을 줄이

는 장점을 지닌다.

삼성전자는 램버스와 협력해 고객사들이 복잡한 칩을 쉽고 빠르게 설계하도록 지원한다. 삼성전자는 2019년 '반도체 2030 비전'을 발표하고 시스템반도체 육성 의지를 밝혔다. 2030년까지 글로벌 1위를 목표로 시스템반도체의 경쟁력 향상을 위한 다양한 활동을 하고 있다.

삼성전자는 2018년부터 파운드리 에코시스템 프로그램 'SAFE™(Samsung Advanced Foundry Ecosystem)'를 운영해 고객들의 설계를 지원했다. 반도체 설계 자동화 툴(EDA) 업체 케이던스와 시놉시스 등을 파트너사로 뒀다.

이듬해 언제 어디서나 즉시 칩을 설계하도록 가상의 설계 환경을 제공하는 SAFE-CDP(SAFE Cloud Design Platform)도 선보였다. 시놉시스의 설계 검증 소프트웨어 ICV(IC Validator)를 비롯해 여러 툴을 제공하고 반도체 성능의 고도화에 따른 설계의 어려움을 덜어줬다. 이와 함께 소량의 칩을 8(200㎜)·12인치(300㎜) 웨이퍼를 이용해 시험 생산할 수 있는 '멀티프로젝트 웨이퍼(MPW·Multi-Project Wafer)' 프로그램을 확대 시행하고 1000억원 규모의 상생 펀드를 조성했다.

신종신 삼성전자 파운드리 디자인 플랫폼 개발실 상무는 "램버스와의 파트너십으로 업계 최고의 메모리 인터페이스 설계 전문 지식과 삼성의 최첨단 공정·패키징 기술이 결합하게 됐다"며 "인공지능(AI)·고성능컴퓨팅(HPC) 등 설계 업체들은 향상된 성능을 갖춘 플랫폼을 구현할 수 있을 것"이라고 밝혔다.