[더구루=오소영 기자] 대만 TSMC가 3차원(D) 패키징 기술을 7나노미터(nm·10억분의 1m) 기반 반도체 양산에 적용하고자 준비 작업을 연내로 마친다. 고급 패키징 기술로 반도체 성능을 강화해 기술 우위를 점한다.

14일 업계에 따르면 TSMC는 '웨이퍼-온-웨이퍼(WoW·Wafer-on-Wafer)'와 '칩-온-웨이퍼-온-서브스트레이트(CoWoS·Chip-on-Wafer-on-Substrate)'의 7나노 제품 인증을 오는 4분기까지 마친다. 두 패키징 기술을 7나노 제품 양산에 잘 적용할 수 있는지를 연말까지 확인하겠다는 뜻이다.

패키징은 가공이 끝난 실리콘 웨이퍼 칩이 훼손되지 않도록 포장하는 공정이다. 외부 습기나 불순물 등으로부터 칩을

보호하고 주기판과 신호를 전달하도록 한다.

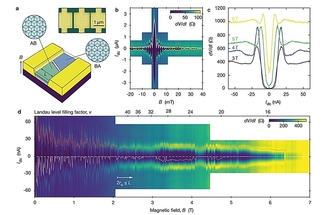

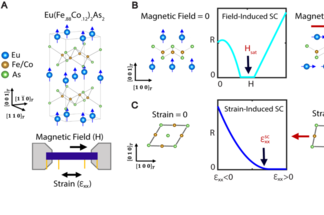

TSMC의 3D 패키징 기술인 WoW는 웨이퍼를 쌓은 뒤 실리콘관통전극(TSV·미세한 구멍을 뚫어 상·하단 칩을 전극으로 잇는 기술)으로 연결하는 기술이다. 단일 패키지에 더 많은 중앙처리장치(CPU), 그래픽처리장치(GPU) 등을 배치할 수 있다.

CoWoS는 인터포저라는 판 위에 메모리와 로직 반도체를 올리는 기술이다. 실장 면적이 줄고 칩 간 연결을 빠르게 할 수 있는 강점이 있다. TSMC가 2012년 처음 선보일 당시 CoWoS는 28나노 칩에 적용할 수준이었지만 7나노까지 대응하도록 업그레이드됐다.

TSMC는 차세대 패키징 기술로 7나노 제품의 성능을 향상시키고 파운드리 시장에서 초격차를 유지한다.

패키징은 반도체 업계의 '새 먹거리'로 떠오르고 있다. 공정 미세화만으로 반도체 성능을 향상시키는데 한계에 봉착해서다. 서로 다른 반도체를 연결하는 패키징 기술로 성능과 전력 효율을 획기적으로 높일 수 있다고 업계는 보고 있다.

TSMC는 3D SoIC(System on Integrated Chips), 통합팬아웃 3D(InFO 3D) 등 차세대 후공정 기술을 개발하고 있다. 작년 8월 고급 패키징 기술을 묶는 플랫폼인 '3D 패브릭(3D FABRIC)' 상표권을 미국 특허청(USPTO)에 제출했다. 이 플랫폼을 적용한 반도체를 자체 양산하고자 후공정 팹도 건설하고 있다.

최근 일본 이바라키현에 패키징 분야를 주로 연구하는 연구개발(R&D) 거점을 짓기로 했다. 미국에도 패키징 공장 투자를 검토 중이다.

시장조사업체 가트너에 따르면 전 세계 패키징 시장은 지난해 488억 달러(약 55조원)에 달했다. 올해 512억 달러(약 57조원)에서 2023년 574억 달러(약 64조원)로 급성장할 전망이다.