[더구루=오소영 기자] 삼성전자가 MBCFET(Multi Bridge Channel FET) 구조를 적용한 3나노미터((㎚·1㎚는 10억분의 1m) 1세대 공정을 시험하고자 암호화폐 채굴용 반도체(ASIC)부터 양산한다. 내년부터 2세대 공정에서 스마트폰 칩 생산에 착수하고 대만 TSMC와의 3나노 경쟁에서 주도권을 잡는다.

11일(현지시간) 시장조사업체 트렌드포스에 따르면 삼성전자는 MBCFET를 접목한 GAA 기반 3나노 공정에서 암호화폐 ASIC를 연내 생산한다.

암호화폐 채굴용 칩은 작고 단순하다. 단가가 높아 30%대 수율에서도 수익을 낼 수 있어 공정 초기 테스트용으로 적합하다는 평가를 받는다. 중국 파운드리 업체 SMIC도 7나노 공정을 시험하고자 캐나다 미네르바 세미컨덕터의 비트코인 채굴 칩을 위탁생산했었다.

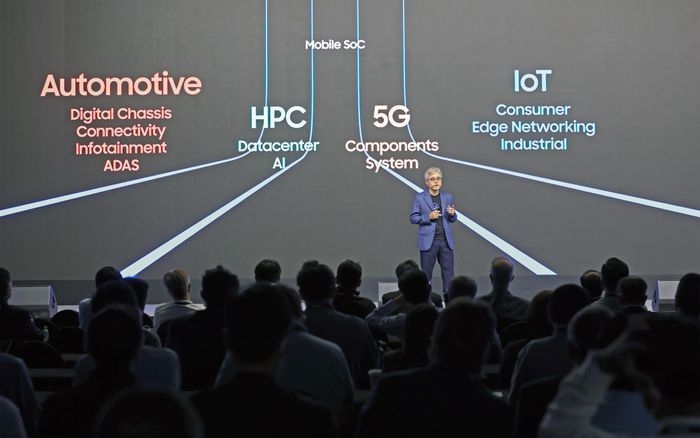

삼성전자는 ASIC 양산을 통해 성능과 전력 소비량, 결함 밀도를 포괄적으로 살핀다. 공정의 완성도를 높여 내년부터 3나노 2세대 공정에서 스마트폰용 시스템온칩(SoC)을 생산할 계획이다. 삼성전자는 앞서 2분기 실적발표 컨퍼런스콜에서도 "3나노 2세대 공정 관련 고성능 컴퓨팅(HPC)과 모바일 부분에서 대형 고객사를 확보했다"고 밝혔었다.

삼성전자는 기술적 우위를 기반으로 수주를 늘리고 TSMC와의 격차를 좁히겠다는 계획이다.

삼성전자는 2030년까지 시스템 반도체 1위로 올라서겠다는 목표를 밝히고 미세 공정 개발에 집중해왔다. 지난 6월 TSMC를 제치고 세계 최초로 3나노 공정 양산을 시작했다. 채널 4면 모두를 게이트가 감싸 기존 핀펫(FinFET)보다 전류의 흐름을 제어할 수 있는 차세대 트랜지스터 구조인 GAA를 선제적으로 적용했다. 단면적을 조절해 성능을 개선하는 MBCEFT 구조도 도입한다. 이를 통해 핀펫 기반 3나노 공정을 택한 TSMC와 차별화를 꾀한다.

미세 공정 개발에도 속도를 낸다. 2025년에 2나노, 2027년 1.4나노 공정에 진입할 예정이다. TSMC는 1.4나노 공정을 준비하는 것으로 알려졌지만 공식적인 로드맵은 아직 나오지 않았다.