[더구루=오소영 기자] 삼성전자가 미국 시놉시스와 2나노미터(㎚·1㎚는 10억분의 1m) 공정에서 반도체 설계 자동화 툴(EDA)을 최적화했다. EDA 파트너와 협력을 강화해 고성능 칩을 개발하려는 고객들의 수요에 대응한다. 동시에 공정 난도가 높아진 2나노에서 수율을 안정화하며 세계 1위 파운드리 회사인 TSMC를 추격한다.

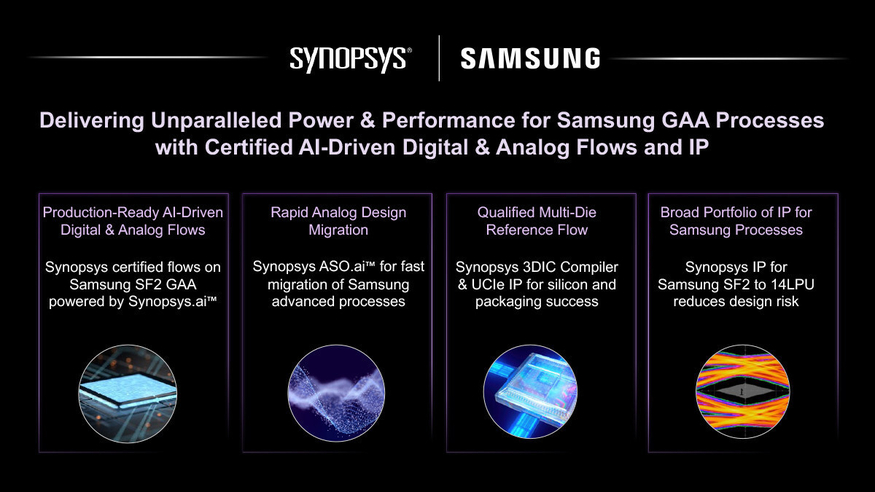

14일 업계에 따르면 시놉시스는 지난 12일(현지시간) 삼성전자 모바일용 1세대 2나노(SF2)와 고성능컴퓨터(HPC)·인공지능(AI)용(SF2Z) 2나노 공정에서 자체 툴인 '시놉시스 ai 풀스텍'을 검증 완료했다.

시놉시스가 제공한 풀스텍은 AI를 활용해 개발된 디자인툴 세트를 뜻한다. DSO.ai™와 ASO.ai™도 여기에 포함된다.

삼성전자는 시놉시스와의 협업으로 고객사가 고성능 칩 개발 기간을 단축하도록 지원한다. 고객사들의 선택 폭을 넓혀 2나노 공정의 경쟁력을 강화한다.

삼성전자는 세계 1위 파운드리 회사인 TSMC와 2나노 공정을 두고 선점 경쟁을 펼치고 있다. 삼성전자는 TSMC와 동일하게 내년 양산을 목표로 잡았다. 최첨단 SF2 공정은 3나노 2세대(SF3) 대비 성능 12%, 전력효율 25% 향상, 면적 5% 감소할 것으로 예상된다.

삼성전자는 지난 2022년 3나노 공정에 도입한 게이트올어라운드(GAA) 기술을 2나노에도 적용해 데이터 처리 속도와 전력 효율을 높인다. 2026년부터 BSPDN(Back Side Power Delivery Network) 기술도 접목한다. BSPDN은 전류 배선층을 웨이퍼 후면에 배치해 전력과 신호 라인의 병목 현상을 개선하는 기술이다.

응용처별 로드맵도 구체화했다. 삼성전자는 2025년 SF2, 2026년 SF2X, 2027년 차량용(SF2A) 개발을 추진한다. 주요 응용처별로 공정 포트폴리오를 갖춰 수주를 꾀한다.

2나노 상용화를 앞두면서 EDA 파트너와도 협력을 강화했다. 2나노는 기존 4~5나노 대비 회로의 선폭이 줄며 탑재되는 연산 장치 수가 늘어난다. 그만큼 설계 단계에서 검증할 요소도 증가한다. 최소 4배에서 최대 10배까지 늘 것으로 추정되면서 안정적으로 양품을 생산하기 위해 EDA 툴의 역할이 커질 것으로 예상된다.

삼성전자는 일찍이 시놉시스, 케이던스 등 글로벌 EDA 업체들과 협력을 다져왔다. 시놉시스와는 2027년 양산 예정인 1.4나노까지 협력을 확대할 것으로 기대된다.

김상윤 삼성전자 파운드리사업부 설계기술팀 상무는 "양사는 고객의 가장 복잡한 설계 요구 사항을 충족하고자 수십 년 동안 긴밀히 협력했다"며 "시놉시스와 달성한 이정표는 상당한 PPA(소비전력·성능·면적) 이점을 제공하며 고성능 컴퓨팅에 대한 업계의 증가하는 수요를 만족시키려는 노력을 입증한다"고 밝혔다.